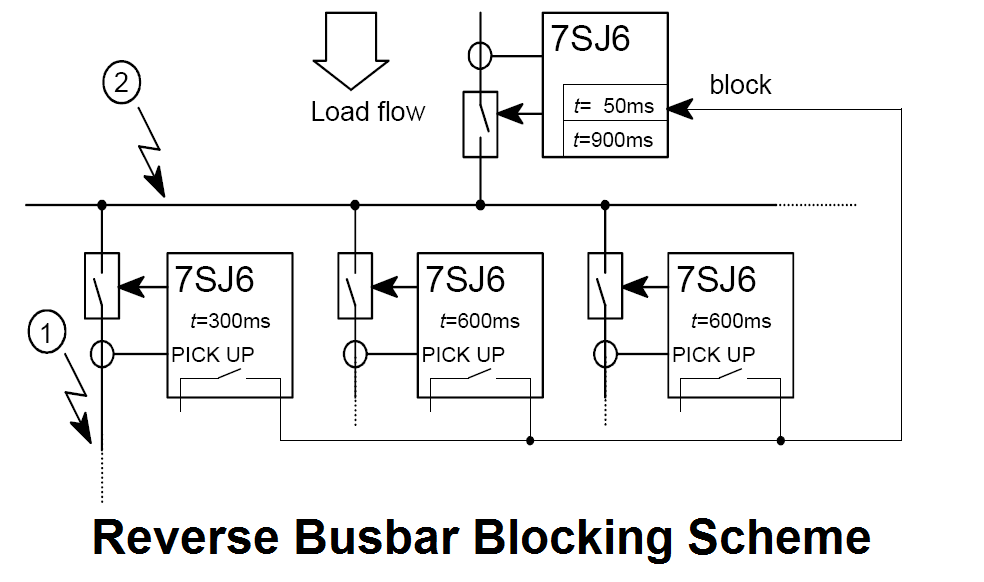

Reverse Busbar Blocking Scheme

The reverse busbar protection is a cost-effective solution for the accelerated clearance of busbar faults in distribution systems. It can only be applied on single busbars with a fixed direction of power flow and fault current flow. In picture 3, a typical application is shown. Overview:For this application, the protection device on the incoming bay […]

Reverse Busbar Blocking Scheme Read More »